存算一体芯片为何兴起

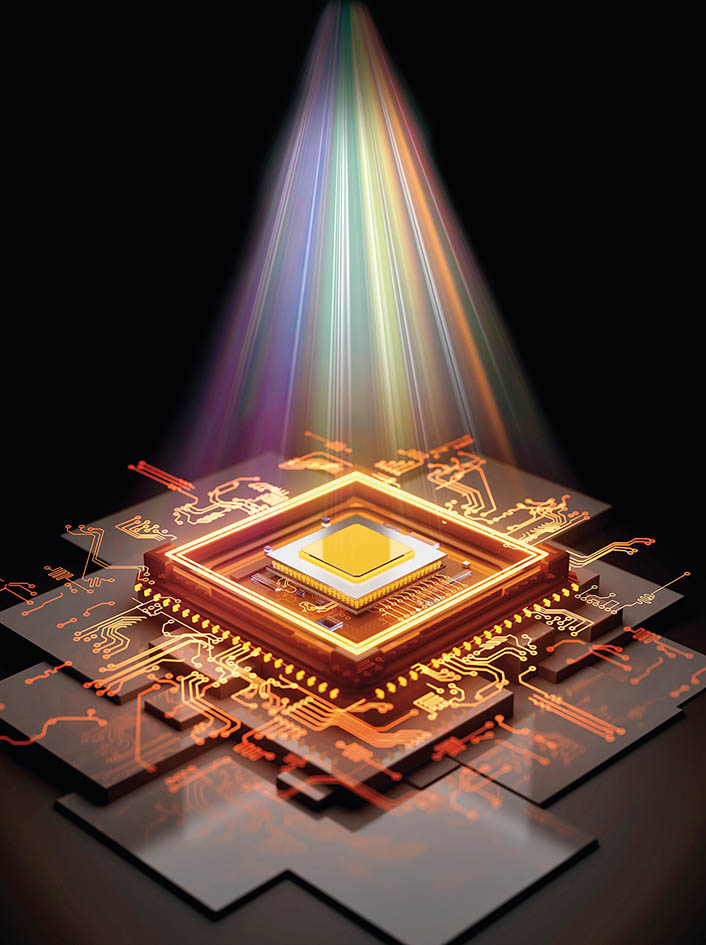

我国科学家研制出首个全模拟光电智能计算芯片

文/陈经

编辑/黄红华

从最初的机械计算机到如今的超级计算机,计算机技术发展已经发生了翻天覆地的变化。即便如此,在面对现代复杂的应用需求时,计算机也开始显露出“力不从心”。

由于传统的计算机架构的数据存储和计算是分开的,数据在存储器和处理器之间的频繁传输导致了延迟,这在某种程度上抑制了计算效率的提高。在这种情况下,将存储和计算功能融为一体的存算一体芯片应运而生。

新技术助推新需求

计算机技术诞生之初,其体系主要依赖冯·诺依曼架构,在这一架构中,CPU(中央处理器)是核心,内存是辅助。

之后相当长一段时间内,计算机系统面对的主要任务,是许多“科学计算”任务,当时业界研究的重点是设计各种精巧的“算法”,加快处理速度,更快输出正确答案。

但到上世纪90年代,有些计算任务如图形显示等已经让CPU难于招架。于是业界开发了GPU(图形处理器)去并行计算显示器上的画面,将宝贵的CPU资源留给操作系统。CPU仍处于计算体系的中心地位,处理用户界面交互、程序算法等众多任务,GPU起辅助作用。

随着计算机体系与应用不断创新,人们对存储和计算性能的要求越来越高,同时还要控制功耗,防止超过限度导致元器件失灵。当前,以大数据、人工智能为代表的新兴技术不断发展成熟,在一些计算任务中,GPU逐渐成为体系核心,而CPU成了辅助。新任务、新要求需要新体系,这也让计算机体系结构出现重大变革契机。

大数据与人工智能相关的新型计算任务往往有三大特征:海量的数据、极多的神经网络计算、巨大的功耗。以近年来流行的大模型训练为例,光是文字训练数据就多达数万G的存储量,需要许多硬盘才装得下;神经网络权重系数上万亿个,往往需要分散在多个硬件内存中;训练耗能极多,电网能力不足无法训练,IT巨头甚至需要自建电网。

CPU对这样的计算任务无能为力,只能沦为配角。由于CPU负责数据搬运、逻辑分支、结果输出等串联辅助任务,主要的计算任务改由海量的GPU阵列完成,每个GPU内部还有成千上万个处理器核心并行计算。

因此,数据与GPU在计算体系的地位上升,例如,一幅图像输入描述具体的问题,海量类似的图像“样例”概括描述问题特性,而训练出来的神经网络权重数据,让GPU的计算结果很好地输出问题答案。

两堵“墙”的阻碍

如果说原来的计算任务瓶颈是CPU能力不足,那么现在的瓶颈变成海量数据的搬运问题。现在流行的计算机架构中,CPU与GPU处理器核心众多,理论上计算能力十分强大,但需要给处理器准备好数据。而海量数据造成了“存储墙”“功耗墙”现象。

“存储墙”,是指内存与CPU、GPU处理器之间通过总线搬运数据,而这是慢速的。处理器算得快,但因为要等待内存数据搬运,因此大量时间处于空闲状态,有时耗时是运算时间的上百倍。比如,处理海量神经网络参数时,需要从内存中先读取,再进行计算。参数规模影响了过程效率,导致主要时间花在从内存搬运数据上,GPU算力利用率非常低(有时不足10%)。

“功耗墙”,是指海量数据需要持续搬运与计算,虽然CPU与GPU理论上能算得过来,但持续工作容易发热聚集,导致硬件温度不断上升,有可能突破界限让元器件在高温中失灵,从而影响计算性能。就像一挺重机枪,不停射击使枪管通红发热,时间一长就没法继续。

从CPU到GPU,主体思路还停留在“正面硬刚”数据搬运和功耗问题上。尽管人们极尽巧思,用各种办法提升数据搬运速度,以及散热、降温,但并不能缓解“存储墙”“功耗墙”问题。

存算一体技术应运而生

为了打破冯·诺依曼计算架构瓶颈,降低“存储-内存-处理单元”过程数据搬移带来的成本,学术界尝试了多种方法。近年来,有不少存算一体技术,已经在计算机产业中广泛应用,如“近存计算”(PNM)。

“近存计算”主要有两种应用:一种由三星、海力士等存储器生产商主导,在内存、SSD(固态硬盘)等存储产品中嵌入定制的计算单元或通用处理器,直接访问计算结果,但计算不能太复杂;另一种是基于先进封装、芯片堆叠等芯片连接技术,由CPU、GPU设计公司(如英伟达、AMD等)主导,将HBM(高带宽内存)围绕GPU裸芯片封装在一起,让处理器以高带宽快速访问数据。目前,这个领域非常活跃,是先进芯片产业前沿,成功应用于人工智能、大数据、边缘计算,在多种计算密集型应用中体现出灵活与高效。

“近存计算”与传统的CPU和GPU架构有所不同,但它仍然是冯·诺依曼架构,属于在传统框架中想办法,是芯片制造与连接封装技术进步,是改良优化传统架构,并非革命。近存计算中,计算与存储还是分离的,虽然比以前“近”多了。

还有一种叫“存内处理”(PIM),出现更早一些,现在也算是近存计算的一类。在DRAM(动态随机存取存储器)或者HBM存储芯片设计时,就在其中内置计算单元,与芯片制造同步进行。在电路中,计算与存储虽然很近,但仍然是分离的,还是传统架构。

值得一提的是,真正突破了冯·诺依曼架构的是“存内计算”(IMC)。如清华大学集成电路学院教授吴华强团队研制的以核心元器件为“忆阻器”的新型芯片,就是“存内计算”技术的代表。

“存内计算”又分为IM-A(In-Memory Array)与IM-P(In-Memory Periphery)两种不同的计算方法。

IM-A是指在元器件内存阵列内部计算,这些计算有特殊的物理原理,直接生成计算结果。这种方法有很好的计算速度和能源效率,因为是光学、电流等物理效应的直接结果。但是结构不够灵活,需要重新设计阵列、修改外围电路。

IM-P是指在外围电路中处理产生计算结果。例如清华大学戴琼海院士与乔飞副研究员团队2023年10月在《自然》杂志发表的光电融合芯片,计算速度非常快、能耗非常低。这个芯片中,光线输入经过透镜组,透镜间的掩码板就相当于新型内存元器件,存储了神经网络权重。而光学模拟运算,生成包含关键信息的少量光学信号,被转换成少量电信号。这些电信号脉冲,在SRAM(静态随机存取存储器)阵列组成的简单外围电路中传播,以模拟的形式输出正确数值。

总之,相比于传统芯片,存算一体芯片优势明显。一些高端的存算一体芯片算力达到了惊人的1000TOPS(处理器运算能力单位)以上,这在传统的冯·诺依曼架构下是难以想象的。在能效方面,存算一体芯片也表现出色。其能效高达10-100TOPS/W(每瓦功率的算力),这不仅超越了传统ASIC(专用集成芯片)芯片,还为未来的绿色和节能计算提供了可能。

由于存算一体芯片在结构上的优化,其成本效益显著,能为企业和研究机构提供更加经济的计算解决方案。随着技术的不断发展和成熟,存算一体芯片将会逐渐走入商业化的轨道。

(作者系风云学会副会长、亚洲视觉科技研发总监)

手机版

手机版